Selecting the Right MLCC for Power Architectures

Learn how to select the right Murata MLCCs for modern power architectures, balancing low ESL, stable capacitance, and smart placement to ensure power integrity in high-speed, high-current systems.

As AI accelerators and high-speed CPUs become the norm in data centers, power distribution networks (PDNs) face a whole new set of challenges. These systems experience fast edges and sharp di/dt events. Cost and performance pressures are demanding denser systems with smaller enclosures.

The result? PDNs need components that can sustain low impedance over wide frequency ranges while fitting into increasingly thin, thermally constrained packages. Multilayer Ceramic Capacitors (MLCCs) are more important than ever!

Fortunately, Murata designed its latest MLCC technologies to sustain power integrity and cut noise at the package and board levels. Their portfolio includes dense, low-inductance, and reliable products, and their application engineering team is always ready to help designers build better, more stable PDNs.

Design Constraints and MLCC Selection

Capacitor selection influences every layer of a system’s electrical behavior.

Today’s engineers face risks around temperature stability, mechanical clearance, and board warpage. Each of these issues adds extra strain on the PDN. Meanwhile, today's high-speed designs introduce frequency-dependent complications that fundamentally change how different parameters interact with the overall system.

When you're working at higher frequencies, equivalent series inductance (ESL) becomes the dominant factor, essentially setting a hard limit on how much current you can deliver. Equivalent series resistance (ESR) plays a major role in how the system recovers from transients and determines energy losses. DC bias effects reduce usable capacitance, leaving engineers with less available charge during rapid load transitions.

Engineers need to define which performance parameters matter for their application. A design for fast di/dt behavior may prioritize low ESL. One that needs bulk storage near the load may target higher capacitance. For strict mechanical envelopes, thin profiles may be better. Each choice influences thermal behavior and long-term reliability.

Murata helps engineers address these trade-offs with a diverse range of material and capacitor options, including X5R, X6T, X7T, and C0G. The company also uses novel internal electrode layouts that cut inductance without reducing volumetric efficiency.

DSC and LSC Strategy

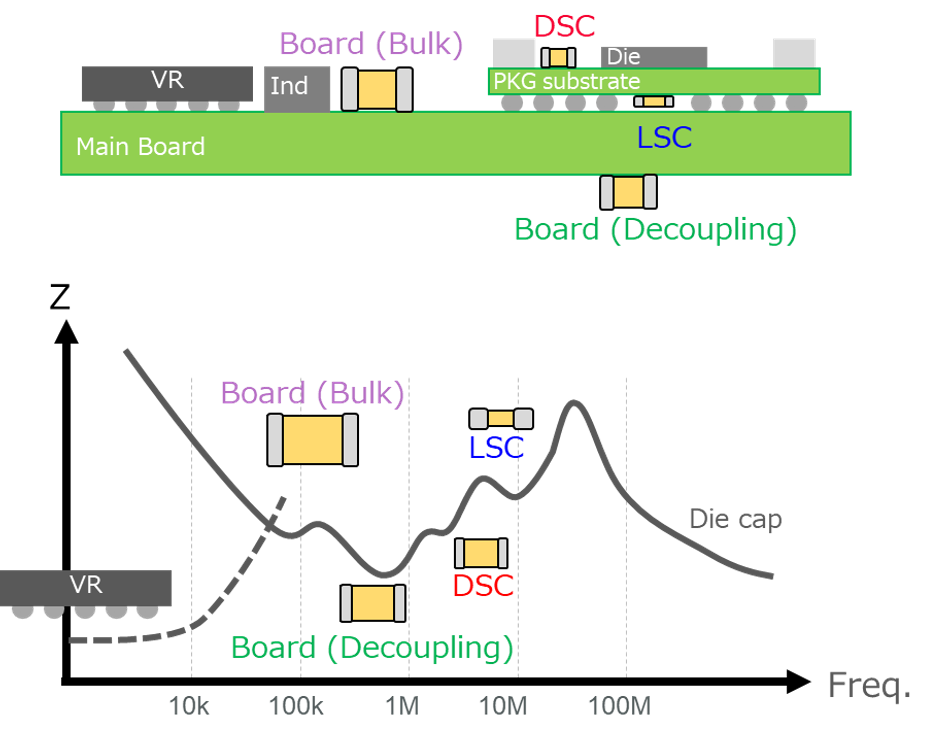

Along with the capacitor type, capacitor placement directly impacts PDN impedance and performance. For example, die-side capacitors (DSC) and land-side capacitors (LSC) support different behaviors. To balance each’s strengths and weaknesses, engineers often deploy them together.

Engineers place LSCs directly beneath the substrate to reduce loop inductance. With close proximity to the load, LSCs provide fast current response at frequencies between 1 and 10 MHz, which helps stabilize the PDN during the first part of a load step. DSCs, by contrast, operate closer to the silicon. They can accommodate thicker, higher-capacitance MLCCs, which supply bulk charge closer to the die power terminals.

Simulation data show that combining DSC and LSC results in a flatter impedance curve, limits anti-resonance behavior, and improves voltage stability during rapid current changes. These benefits become increasingly important as processors adopt higher currents and wider bandwidths.

Murata offers a lineup of low-ESL capacitors that are particularly well-suited to these mixed topologies. Their reverse-geometry LLL parts and multi-terminal NFM and LLF parts reduce routing length and lower total inductance. The result is a PDN that holds voltage through both fast and sustained load changes. Engineers can also tune DSC and LSC placement to match the regulator's switching profile and the silicon's power demands.

Structural Advances for Low ESL MLCCs

ESL originates from the length of the internal electrode path and the way that path couples to external terminals. Murata reduces both factors through geometric reorientation and multi-terminal routing.

Standard MLCCs conduct current along the long axis, which produces longer current paths and higher self-inductance. In contrast, Murata's reverse-geometry LLL series capacitors rotate the electrode orientation to shorten the current loop. As a result, the LLL series cuts inductance to almost one-third that of a standard MLCC, allowing them to deliver fast current during early transient phases.

The three-terminal capacitors in the NFM series by Murata push ESL even lower with parallel-operating dual return paths. The NFM architecture reduces overall loop inductance to almost one-tenth of a conventional MLCC and produces a smoother transition between ESR- and ESL-dominated regions.

Finally, four-terminal capacitors in the LLF series extend these gains with a symmetric electrode layout. As current can enter and exit from all sides, the device minimizes loop area and magnetic coupling. With standard 0.6 x 0.6 mm footprints, LLF parts fit tight land-side placements and maintain high capacitance while improving high-frequency response.

Regardless of the family type, Murata’s unique MLCC structures help engineers meet their impedance targets with fewer capacitors.

Selecting for System-Level Optimization

A stable PDN requires a complementary mix of capacitors. PDNs need high-capacitance MLCCs to deliver bulk energy and support later stages of a transient. At the same time, they require low-ESL capacitors to suppress high-frequency current spikes and control anti-resonance behavior. System designers should combine the different types to create a PDN that maintains voltage over a wide frequency range and supports dynamic load profiles.

Murata’s SimSurfing platform helps engineers optimize this mix. It models real behavior under temperature, voltage, and bias conditions to output effective capacitance and S-parameter data that drop directly into PDN or full-system simulations. These outputs give designers a clear view of impedance, stability, and high-frequency routing effects.

Engineers can also use myMurata to compare products, study mechanical reliability, and evaluate construction options. The platform shortens selection time and improves the link between PDN modeling and physical layout.

With Murata’s library of standard and multi-terminal low-ESL MLCCs, engineers can find the right mix of elements to flatten impedance, reduce noise, and support faster switching speeds.

Murata has the MLCCs

As system frequencies rise and transient demands intensify, MLCCs are becoming more important. Luckily for engineers, Murata continues to develop its MLCC technologies in tandem with the demands of modern computing architectures. With lower ESL, thinner profiles, and consistent capacitance under bias, Murata’s lineup helps engineers build the next generation of power-efficient, high-speed hardware.