Designing in Milliwatts: Rethinking Compute Architecture with the Electron E1 Processor

Traditional processors are inefficient in certain contexts, wasting energy on data movement rather than computation. As a result, the industry is shifting focus to maximizing performance per watt, highlighting the need to rethink compute architecture to meet real-world constraints.

Modern compute systems are constrained less by what they can do and more by what they can sustain. From edge sensing devices and industrial wearables to data centers and space systems, the boundaries of what engineers can build are defined by power, thermal limits, and system longevity. In other words, energy is the fundamental constraint.

As demand grows for AI-driven functionality in embedded and remote systems, engineers must deliver more capability within shrinking power and thermal budgets. At the edge, devices must operate for months or years without maintenance. In space, energy is limited, heat dissipation is difficult, and reliability must be engineered into every component.

Traditional processors are not built for this context. They are designed to run general-purpose workloads across a wide range of applications, often to remain compatible with software written decades ago. As Efficient Computer describes it, conventional CPUs “are overdesigned for generality”.This approach has led to architectures that are large, complex, and power hungry. Much of the energy consumed goes not into useful computation but into internal data movement and instruction control.

The result is a growing mismatch between the capabilities of modern compute systems and the physical limitations of their deployment environments. The industry is now reaching the point where performance per watt has become the defining metric. The question is no longer how much raw power a processor can deliver, but how efficiently it can do the work that matters within the limits of real-world systems. This shift demands a rethinking of compute architecture.

Compute Design Reconsidered

If energy defines the limits of modern compute systems, then architectural design must treat efficiency as a first principle. With the rise of embedded and remote applications, the goal has become sustained performance in environments where power is scarce, heat must be avoided, and resilience matters as much as speed.

This reframing exposes the limits of current strategies. Many modern SoCs try to save power with fixed-purpose accelerators, but workloads change faster than hardware can. When an accelerator does not match the task, execution falls back to a power‑hungry CPU core, leading to dormant hardware and unrealised energy efficiency.

Efficient Computer approaches this problem from first principles. This US‑based chip startup is building a new class of processors for systems that must deliver high‑value compute within strict energy, thermal, and reliability constraints. Its first product, the Electron E1 processor, is the world’s most energy-efficient, general-purpose system-on-chip. Designed for battery‑powered, embedded, and remote deployments, the E1 processor pairs ASIC‑class efficiency with general-purpose programmability.

The Electron E1 processor runs complete applications with exceptional energy performance. Neural networks, digital signal processing, graph analytics, compression, and cryptography all execute locally without reliance on narrow accelerators or cloud offload. The result is responsive, private, and reliable compute where power is limited, and connectivity is unreliable or unavailable.

These capabilities rest on Efficient’s proprietary Fabric architecture. Programs execute as dataflow graphs across a spatial compute array, eliminating much of the control and hierarchy overhead found in conventional processors. The Electron E1 processor moves the compute closer to the data. Products can process information locally, efficiently, and intelligently. For designers facing hard limits on space, heat, and power, it opens a path to embedded intelligence that was previously out of reach.

The Architecture That Makes It Possible

The Fabric architecture behind the Electron E1 processor is an energy-minimal dataflow architecture. It implements spatial parallelism and a distributed structure of Processing Elements (PEs) that eliminates much of the overhead found in traditional CPU designs. Each PE executes operations as soon as data is available, following a data-driven execution model. Instruction memory is distributed throughout the Fabric network in the form of bitstream caches.

The design avoids speculative execution, global clock distribution, and deep cache hierarchies. Simplicity lowers leakage current and switching activity, two primary sources of wasted power. Direct tile‑to‑tile links keep communication short and predictable, which tightens performance control and eases timing closure.

To support complete applications on‑device, the Electron E1 processor integrates fast local memory and rich peripherals within the same low‑power envelope, as shown in the table below.

Feature | Purpose |

4 MB MRAM | Holds firmware and large data sets on‑chip, eliminating high‑energy off‑chip storage accesses |

3 MB SRAM | Provides fast working memory for Fabric tiles without the power cost of external DRAM |

128 KB cache | Captures temporal data reuse, reducing tile‑to‑tile traffic and further cutting energy per operation |

Six UART ports | Connects to sensors or radios with minimal protocol overhead and predictable timing |

Six QSPI masters | Streams high‑bandwidth data, such as camera frames, into Fabric without external DMA logic |

Six SPI‑slave interfaces | Provides high‑speed host communication without extra bridge logic or power overhead |

Six I²C masters | Manages low‑speed peripherals and configuration buses while keeping wiring simple |

Seventy‑two GPIOs | Offers broad digital I/O without extra expanders, saving board area and leakage current |

On‑chip RTC | Enables precise wake‑sleep scheduling for long duty cycles without an external timer |

Programmable power‑management unit | Dynamically scales voltage and frequency, matching energy use to workload demand |

Integrated regulators and clock generation | Removes external PMIC and oscillator components, shrinking PCB footprint, and lowering total system power |

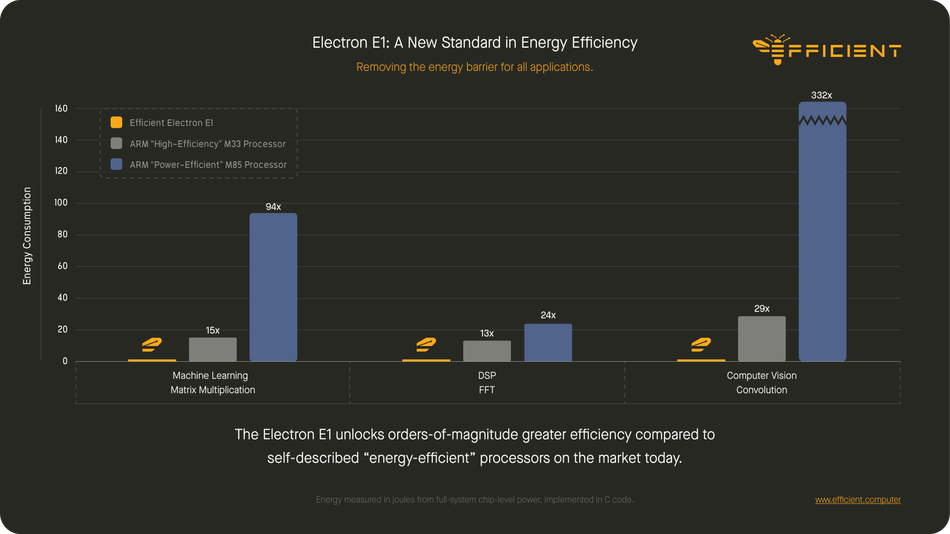

The Electron E1 processor delivers up to 100x the energy efficiency of conventional low-power CPUs and can operate for years on small batteries or harvested power. This is the foundation that allows engineers to deploy local intelligence where it was previously not feasible.

The Electron E1 processor and effcc Compiler are built from the ground up to deliver radically better energy efficiency for general-purpose computing applications. Our spatial dataflow design means that developers no longer have to choose between efficiency and generality. With this release, we’re enabling the next generation of energy-constrained computing applications and devices.”—Brandon Lucia, Efficient Computer, CEO.

Architecture and application are inseparable. In sealed industrial enclosures, reduced data movement limits heat rise and allows fanless designs. In orbit, deterministic operation and low leakage support reliable missions under tight power budgets. The Electron E1 processor shows that when efficiency becomes the design foundation, intelligent systems can live where power, heat, and maintenance once stood in the way.

Software That Meets Developers Where They Are

Energy‑first hardware delivers value only if the software path is clear. Efficient Computer built that path in parallel with the silicon through the effcc® Compiler, a dataflow compiler that maps conventional code onto the Fabric processor with speed and precision.

The effcc Compiler is fully compatible with standard C, allowing developers to work within familiar toolchains; upcoming releases add ONNX, C++, Python, and Rust. Developers stay inside existing toolchains while effcc replaces GCC or Clang in the build flow. Compilation completes in seconds, giving teams rapid feedback without FPGA‑style synthesis delays.

The effcc Compiler automatically transforms high-level code into a dataflow graph, mapping it onto the Fabric architecture with optimizations for locality and parallelism. There is no need to learn a new programming language. As one of Efficient’s engineers put it, “The effcc Compiler takes your code, converts it into a dataflow graph, and optimizes it for maximum efficiency on the Fabric processor.”

Among the core technologies powering the effcc Compiler is MOF®, an optimizer that analyses where a program spends energy and restructures it as a dataflow graph tuned for Fabric. It exposes parallelism, places data close to compute, and selects the lowest‑energy execution pattern without requiring manual refactoring.

The surrounding toolset includes a drop‑in debugger, a functional simulator, and power‑estimation utilities. Together, they let developers move from initial compile to energy profiling in a single workflow.

This has practical implications for teams working in embedded applications:

● An industrial wearable running multiple AI models keeps its full feature set because each inference passes through Fabric with minimal overhead.

● A field robot executes local decision logic all day on a modest battery and stays cool enough for sealed housing.

● A remote sensor stack blends signal processing and compression on‑device, trimming wireless data volume and extending battery life.

The effect turns the Fabric into a ready target for production software, rather than a research platform. Teams can bring existing code, iterate fast, and deploy systems that meet strict power and thermal budgets without trading away capability.

Design Stories in the Field

Architecture earns its value when it expands what engineers can build. The three examples below show where the Electron E1 processor delivers capabilities that were previously out of reach.

Industrial Automation

Industrial sensors and embedded controllers often sit inside sealed housings where batteries must last for years, and heat has nowhere to escape. The Electron E1 processor lets these nodes perform vibration analysis, sensor fusion, and anomaly detection locally, sampling at high rates without overrunning the energy budget.

A single battery or an energy harvesting module is enough to power continuous inference, while the chip’s deterministic timing keeps results predictable for maintenance planners. Real computation now lives inside spaces once limited to simple threshold triggers.

Space Systems

Space-grade computers must be radiation-tolerant, power-efficient, and highly reliable. The deterministic, low-leakage nature of the Fabric architecture reduces complexity and failure points.

Whether embedded in a CubeSat, a planetary lander, or a high-orbit surveillance platform, the Electron E1 processor reliably provides attitude determination, image compression, and autonomy functions in milliwatts, easing thermal design and extending mission life when solar input is low. Engineers gain general‑purpose processing without the mass and power penalties that usually accompany reliability in space.

Industrial Wearables

Computer vision, environmental sensing, and AI-assisted feedback are becoming standard in industrial safety and productivity gear. The challenge is to fit these capabilities into wearable devices that must be lightweight, safe, and battery-efficient.

The Electron E1 processor runs multi-modal AI models at the edge of the network, tracking hazards or worker fatigue in real time while remaining under human-safe surface temperatures. A full work shift on a small lithium‑ion battery is realistic, and the absence of bulky heat sinks keeps devices comfortable and unobtrusive. Concepts move from lab demo to field deployment without a trade‑off between intelligence and ergonomics.

Deployment, Design Guidance, and What Comes Next

The Electron E1 processor has been engineered for integration into embedded and robotics systems with minimal friction. In typical operation, the chip operates in milliwatts, and its thermal profile stays within the limits of sealed enclosures and body‑mounted wearables. The on-chip power-management unit, integrated regulators, and local clock generation reduce board complexity.

The roadmap builds on the same principle that shaped the first device: energy is the anchor, not an optimization pass. The Fabric architecture scales horizontally across multiple chips for higher throughput. Future releases will retain programmability, efficiency, and simplicity as first-order principles.

For engineers who live with tight limits on power, space, and maintenance, the choice of architecture defines what’s possible. By cutting wasted data movement and aligning compute with the available energy, the Electron E1 processor turns constraints into design headroom. Systems that once relied on cloud resources or custom ASICs can now run locally, efficiently, and with room to evolve.

To learn more about the Electron E1 processor, the Fabric architecture, or the effcc Compiler, visit Efficient Computer and join the product launch program.

References

1. A. Shilov, “Startup aims to make CPUs 100x more energy efficient with ‘reconfigurable’ chips - Efficient Computer reveals…,” Tom’s Hardware, Mar. 08, 2024. [Online]. Available: https://www.tomshardware.com/pc-components/cpus/startup-aims-to-make-cpus-100x-more-energy-efficient-with-reconfigurable-chips