From Chaos to Clarity: A Roadmap to AI-Ready Design Data

Engineering teams can achieve AI-ready design data with five-level maturity model by Keysight. The unified, traceable data accelerates design cycles, boosts IP reuse, and reduces costly re-spins.

AI-Ready Design Data Processing

AI in electronic design automation (EDA) is only as good as the design data it consumes. Yet for many engineering organizations, the path to AI remains blocked. The challenge is not that algorithms are unavailable, but that design data is fragmented, poorly versioned, and inconsistently documented. In this environment, AI amplifies noise instead of delivering clarity.

Drawing on Keysight Technologies’ industry-wide survey of more than 900 design professionals — conducted to assess the state of design and IP data management across sectors such as semiconductors, automotive, and telecommunications—this whitepaper presents a five-level maturity model for achieving AI readiness. It provides design and engineering teams with a roadmap for moving from ad-hoc file handling and siloed design practices to unified, traceable, and automated data management.

Backed by Keysight’s decades of experience in electronic design workflows, the model defines measurable milestones and actionable steps that lead to tangible outcomes: faster design cycles, fewer costly re-spins, higher reuse of intellectual property (IP), and traceability that supports safety and compliance without slowing innovation.

In this white paper, you will learn:

- Why AI struggles with messy design data: Understand the hidden barriers that prevent AI from delivering value in design workflows and how fragmented data undermines automation.

- The five levels of design data maturity: Learn how to progress from chaotic local folders to a fully AI-ready infrastructure, with clear milestones and actionable steps at each stage.

- Real-world challenges and solutions: Explore how companies in semiconductors, automotive, and telecom are overcoming data chaos to achieve faster cycles, better reuse, and compliance.

- Keysight’s proven approach: See how Keysight’s SOS platform support each stage of the journey with EDA-aware version control, IP catalogs, and integrated documentation.

- How to recognize when it’s time to level up: Identify the signs that your organization is ready for the next.

Why AI Stalls on Messy Design Data?

Across design-intensive industries such as semiconductors, automotive, and telecom, teams are exploring how AI can accelerate design verification, automate IP recommendations, or guide engineers toward better reuse decisions. In theory, these tools promise to reduce development cycles and cut down the repetitive manual work that slows projects. In practice, however, most teams find that their design data environments are too disorganized to support AI.

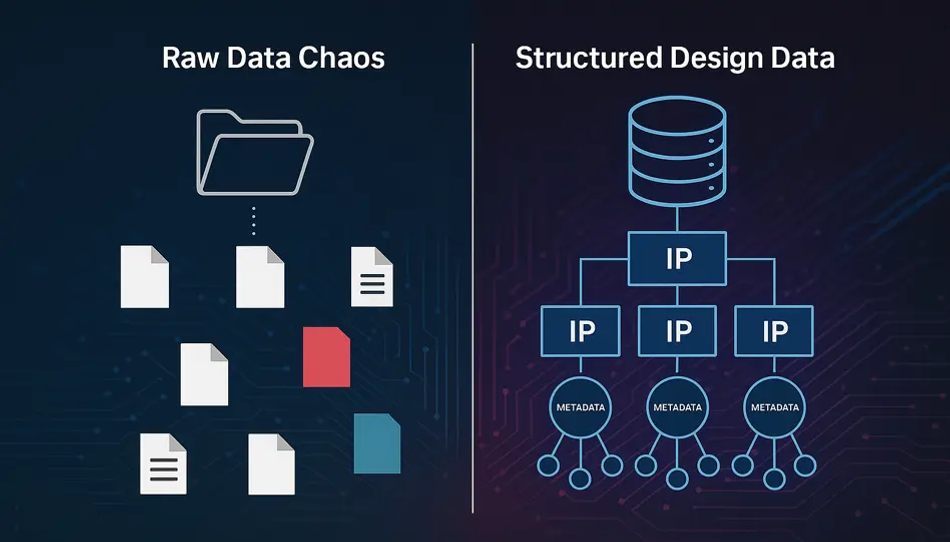

The real barrier lies in the state of the underlying data. Designs are scattered across local directories, dependencies are tracked in spreadsheets or overlooked entirely, and documentation trails vanish into email threads or shared drives. What should form the foundation for AI ends up undermining it, leaving teams with fragmented information that cannot support advanced automation.

To address this, teams need to approach data readiness as a staged maturity curve. The journey runs from unmanaged folders to enterprise-wide, governed data, and finally to fully AI-ready infrastructure. Each stage builds the discipline that enables the next. Once data is unified, traceable, and contextual, the same system that reduces chaos also generates a clean corpus for machine learning and analytics.

“AI adoption in design begins with data that is consistent, traceable, and ready to be trusted. When teams establish this foundation, they create the conditions for automation, faster collaboration, and more reliable outcomes.”

— Pedro Pires, Product Manager at Keysight

The Hidden Cost of Data Chaos

The costs of unmanaged design data are rarely visible on a balance sheet, yet they accumulate with every project. Engineers report that nearly 29 percent of their time is consumed by tracking dependencies, which involves tracing the versions of IP blocks, verifying the current status of third-party licenses, and resolving integration conflicts across subsystems. This manual work drains schedules and leaves compliance to chance.

Storage inefficiencies are another quiet drain. In many teams, each engineer maintains a full local copy of vast binary repositories. Keysight’s survey shows that 60 percent of respondents recognize storage waste as a serious issue. The cost is in both the terabytes consumed on high-performance storage and the friction engineers face in day-to-day work. Cloning multi-gigabyte repositories saturates networks, slows synchronization, and leaves engineers waiting when they should be designing.

Documentation provides yet another weak point. More than half of respondents admitted that documentation is rarely kept in sync with design data. In practice, this means that critical integration details are scattered across emails or never captured at all. Engineers tasked with reuse cannot trust older IP because the documentation is missing or outdated. When designs must meet safety or compliance standards, these gaps translate directly into delays and risk.

Meanwhile, industry trends amplify the challenge. Teams are performing more simulations than ever before, generating vast new datasets of waveforms, models, and results that must be correlated to design versions. Chiplet-based architectures add layers of interdependence, where each IP must be tracked across projects and suppliers. And safety and export regulations demand end-to-end traceability, requiring organizations to prove the lineage of every design decision.

The cumulative result is a system where engineers spend more time wrangling files than creating designs. It is a world in which AI cannot function because there is no structured foundation for learning or automation. These growing pressures make it necessary to chart a clear progression in how design data is managed.

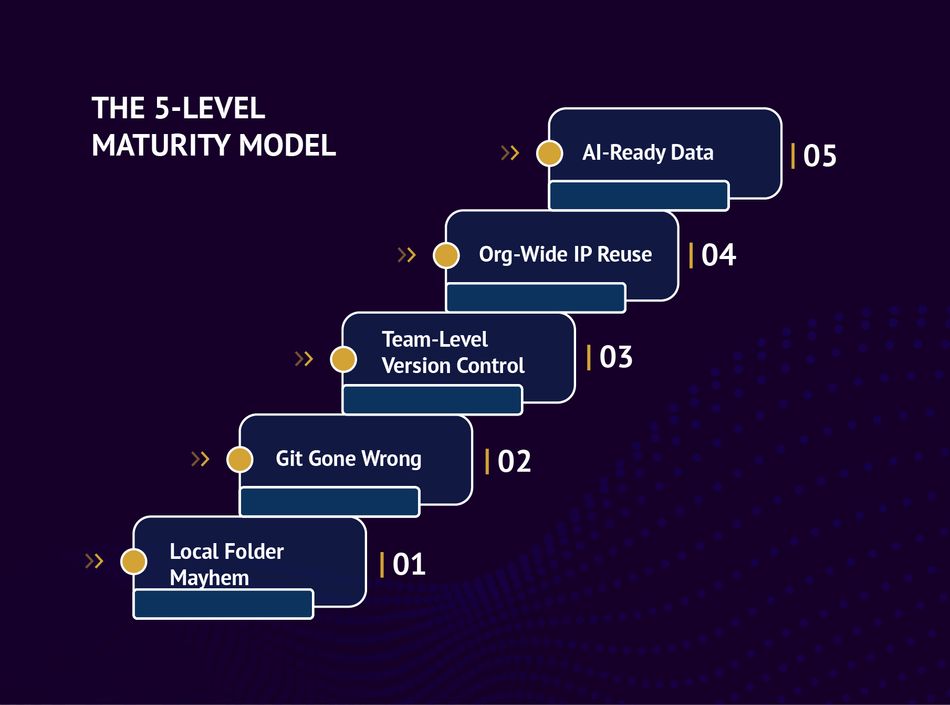

The Five Levels of Data Maturity

A practical way to approach this journey is to view it as a staged progression in data maturity. The maturity curve for design data describes five stages — each level addresses a distinct set of practices, risks, and capabilities. Together, they provide a roadmap for teams moving toward AI readiness.

Level 1: Local Folder Mayhem

At the lowest level, design data lives in per-engineer folders, often with ad-hoc naming conventions and no common repository. Files are emailed between colleagues, with no authoritative version. IP blocks may be reused informally, but their provenance is undocumented.

Duplicate work, inconsistent results, and the absence of an audit trail quickly become the defining risks at this stage. Knowledge transfer is dependent on tribal memory, making teams brittle when engineers move on. At this level, even basic collaboration is costly.

Starter actions focus on building the first layer of discipline: move data into a shared repository root, establish naming standards, and require minimal check-in notes tied to tasks. While primitive compared to later levels, these practices at least create a shared baseline and provide the first traceable steps in a design history.

Level 2: “Git Gone Wrong”

In many organizations, the first attempt at improvement is to adopt software-style version control, such as Git or Subversion. These tools excel in software environments but falter in hardware design. EDA workloads involve massive binary files that cannot be diffed or merged. Teams often struggle with broken repositories, lockouts, and a reliance on spreadsheets for dependency tracking.

The result becomes brittle reuse. Merge conflicts on non-mergeable binaries are frequent, and context on design hierarchy is lost. What was intended as structure becomes another form of chaos.

At this level, teams should begin cataloguing their most-used IP blocks, introducing exclusive-edit policies for binary objects, and mapping critical dependencies. While the tools may not be well-suited, the cultural discipline of tracking and documenting assets lays the groundwork for the next stage.

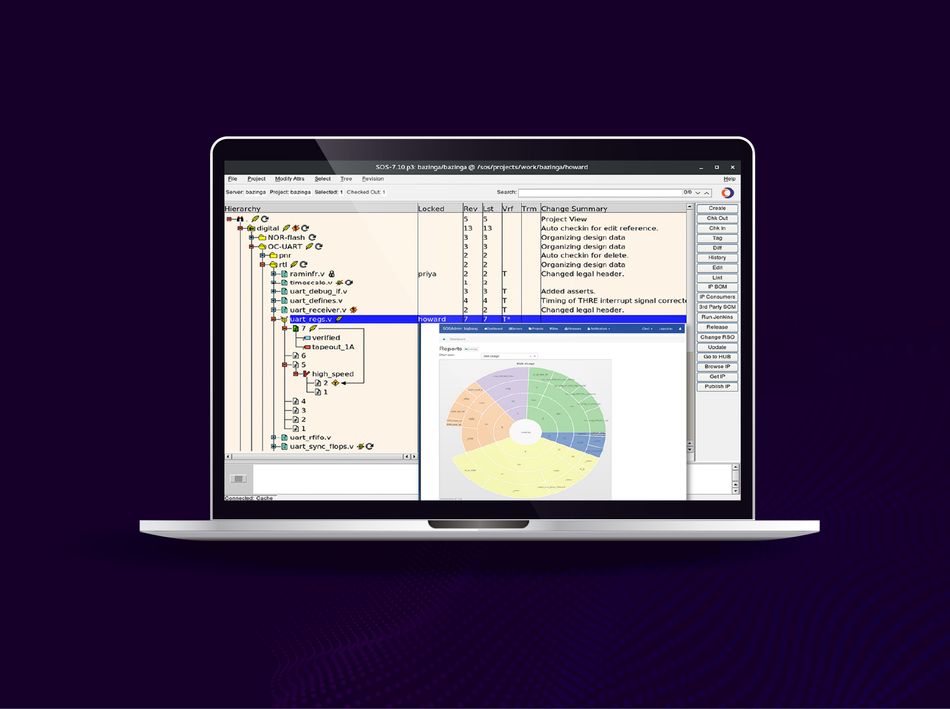

Level 3: Team-Level Version Control (EDA-Aware)

True progress begins with systems designed for hardware design data. An EDA-aware version control environment, such as Keysight SOS, provides a centralized repository that handles large binary files through workspace-based synchronization. Engineers pull only the data they need and, thus, reduce storage duplication.

Exclusive check-outs prevent conflicting edits on binaries, while visual design diffs highlight schematic or layout changes. These capabilities enable predictable reviews and minimize cross-team breakage. By integrating directly into familiar design environments like Cadence Virtuoso or Keysight

ADS, the system fits into the engineer’s workflow rather than disrupting it. At this stage, teams gain a sense of stability as the repository becomes the trusted source of design data and the system itself begins to guide collaboration and governance.

Level 4: Org-Wide IP Reuse and Dependency Awareness

Once version control is stabilized, the focus shifts to organizational reuse. An enterprise IP catalogue becomes essential. Keysight SOS provides metadata, usage lineage, dependency graphs, and license tracking. Every IP block, whether internal or third-party, is documented with its history, verification status, and associated documentation.

This enables where-used impact analysis. If an IP block contains vulnerability, teams can immediately see which projects are affected. If a specification changes, engineers know which designs need to be re-verified. Reuse becomes consistent because teams trust the data.

The shift at this level is felt in shorter development cycles and more predictable outcomes, as trusted data supports reuse across sites and extends collaboration from individual teams to the wider organization, including suppliers through controlled sharing mechanisms.

Level 5: AI-Ready Data

The final stage unifies all design and IP data under consistent identifiers, with traceability from requirements through verification and release. Lineage queries are automated. Simulation and test data are correlated to specific design versions. Clean datasets can be fed into machine learning models to recommend compatible IP, flag stale dependencies, or optimize verification workflows.

Reaching this level requires a platform that can scale to manage terabytes of design data and support synchronization across global sites. It must also connect with PLM and issue trackers while enforcing role-based controls to meet standards such as ISO 26262. Keysight SOS has demonstrated these capabilities, combining centralized storage optimization, visual diffs, dependency intelligence, and integrated documentation into a unified infrastructure.

The maturity reached here means design lineage can be queried instantly, and simulations remain tied to the exact revisions that produced them. Hence, engineers can begin to trust their data as the raw material for machine learning.

How to Know It’s Time to Level Up?

Organizations rarely move smoothly through these levels. They progress in bursts, often triggered by specific pain points. Recognizing the signs is critical to deciding when to invest in the next stage.

Teams stuck at early stages often experience unexplained failures when dependencies shift silently. What appears as a “mystery breakage” is usually the result of an IP change that was never tracked. Other warning signs come from storage growth per engineer. When every new hire adds terabytes of duplicated data, the model becomes unsustainable. Design reviews provide yet another signal; if sessions stall because documentation is missing or outdated, the organization is overdue for change.

Triggers to upgrade also come from external pressures. Expanding to cross-site collaboration or involving suppliers introduces complexity that local or ad-hoc systems cannot manage. Safety and regulatory programs such as ISO 26262 mandate full traceability, forcing teams to adopt governed data systems. New chiplet and heterogeneous designs create deeper dependency graphs, making manual tracking impossible.

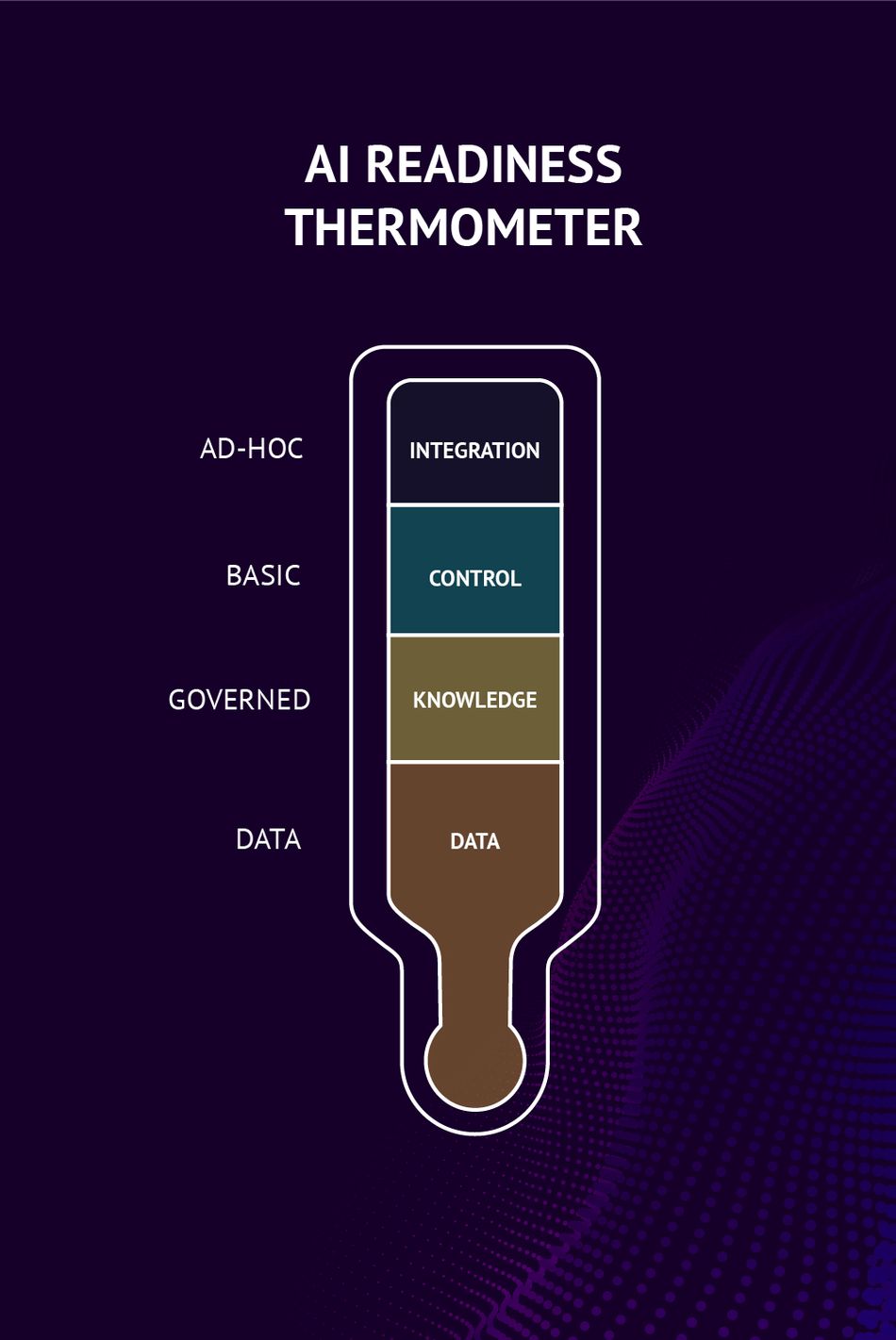

An AI-ready organization looks very different:

- Its data plane is centralized and storage-efficient, with workspace pulls and site proxies to minimize network strain.

- Its control plane enforces exclusive locks for binaries, provides visual diffs, and governs releases.

- Its knowledge plane maintains an IP catalogue with dependency graphs and integrated documentation.

- Its integration plane ties all of this into the engineer’s native tools, as well as PLM and issue trackers, ready to scale into the cloud.

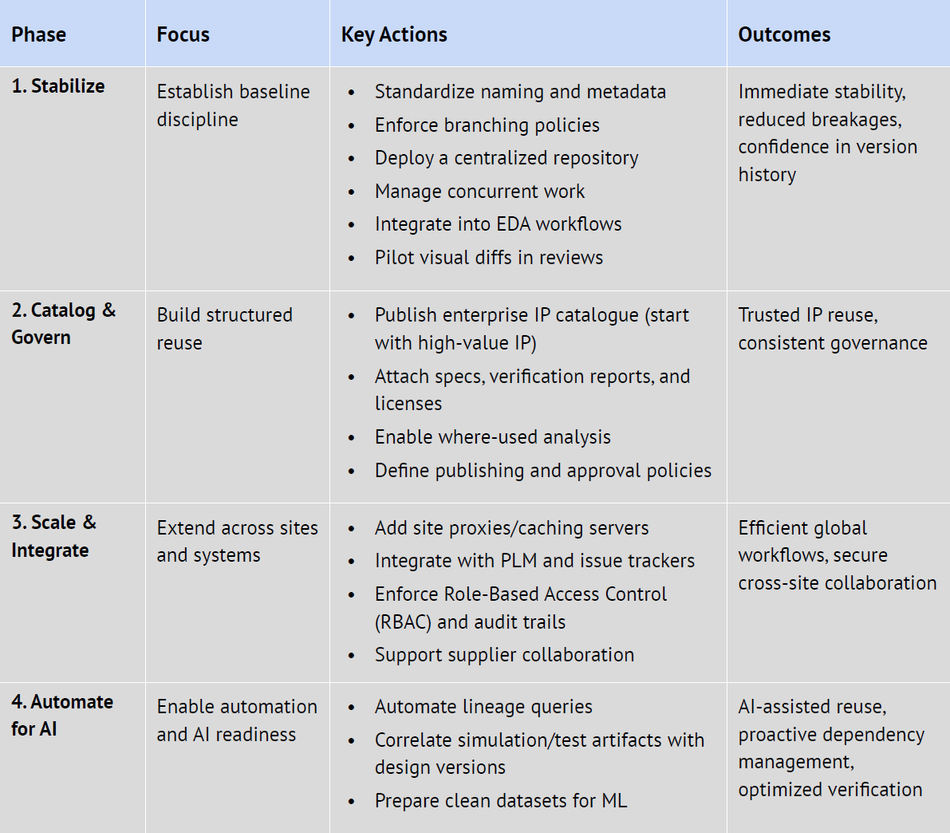

Implementation Roadmap

Moving along the maturity curve requires a phased approach. Attempting a big-bang transformation risks overwhelming teams and derailing active projects. A structured roadmap, as shown in the table below, provides a safer path.

Table 1. Implementation Roadmap

Industry Snapshots

The path to AI-ready design data looks different across industries, but the challenges of version control, IP reuse, and traceability are shared. The following examples illustrate how organizations in semiconductors, automotive, and telecommunications are applying the maturity model in practice and what outcomes they achieve as a result.

Semiconductors

In semiconductor design, system-on-chip (SoC) projects involve dozens of teams and hundreds of IP blocks. Without centralized management, duplication is rampant and re-spins are frequent. Leading companies have adopted enterprise IP catalogues and EDA-aware version control to unify their analogue, digital, and RF groups in a single environment.

With a system like Keysight SOS, validated IP blocks can be shared across sites with their documentation intact. Engineers gain confidence that they are using the correct versions, and integration proceeds without the risk of reusing obsolete assets. The result is faster schedules and improved quality, as traceability ensures that specification changes are consistently implemented. In semiconductor programs, each re-spin carries a steep price in both budget and time, making disciplined data management a direct safeguard against wasted effort.

Automotive

Automotive electronics face the dual challenge of innovation and compliance. Advanced driver assistance systems (ADAS) and safety-critical ICs must meet ISO 26262 standards, requiring exhaustive traceability of every change, review, and test. Traditional design data practices cannot provide this level of visibility.

By implementing Keysight’s ISO 26262-certified data management platform, automotive teams maintain a full history of every IP and design revision. Verification results and requirements are linked to specific versions, making compliance audits straightforward. Access control features partition safety-critical IP, preventing interference from unrelated teams. Supplier collaboration is enabled through controlled hubs, replacing risky ad-hoc file transfers. The outcome is a system where innovation in electric and autonomous systems proceeds without compromising compliance.

Telecommunications

Telecommunications hardware evolves at a pace few other industries can match. Standards shift rapidly, and each new generation requires vast amounts of simulation and test data. Teams must manage FPGA prototypes, ASIC revisions, and performance validation across countless scenarios.

Keysight’s integrated solution addresses this by linking design data with downstream test data. Teams work from a single source of truth, correlating design files, simulation outputs, and test results in one platform. IP blocks from multiple sources, such as DSP cores or encryption engines, are tracked and licensed consistently across variants. The result is a workflow where engineers spend less time wrestling with data, integration errors are minimized, and development cycles move quickly enough to keep pace with 5G and 6G demands.

Conclusion

Design data management is often overlooked compared to tools and algorithms, yet it forms the foundation for everything that follows. Without discipline in how data is stored, versioned, and traced, AI cannot deliver on its promises.

The five-level maturity model outlined here provides a roadmap from local chaos to AI readiness. Each step builds the practices and infrastructure that enable the next. By the time organizations reach unified, traceable, and automated data, they are ready not just to adopt AI, but to trust it.

Keysight’s SOS platform embodies this progression, providing the capabilities required at each stage: from version control tailored to EDA, to enterprise IP catalogues, to integrated documentation and dependency tracking. Organizations in semiconductors, automotive, and telecom are already proving the benefits in faster cycles, reduced risk, and greater innovation.

The path from chaos to clarity is available today. For engineering leaders, the choice is no longer whether to embark on it, but how quickly.

Get in touch with Keysight’s experts to explore how your teams can advance on this maturity model and identify the first steps that align with your organization’s design priorities.